Digitaalisen laitteiston suunnitteluprosessi on muuttunut voimakkaasti viime vuosina. Joten pienet digitaaliset piirit voidaan toteuttaa käyttämällä PAL- ja PLA-piirteitä. Jokaista laitetta käytetään toteuttaa erilaisia piirejä jotka eivät tarvitse enempää kuin tietyssä sirussa tarjottujen i / ps-, o / ps- ja tuotetermien lukumäärä. Nämä sirut eivät riitä melko vaatimattomiin kooihin, ja ne tukevat yleensä enintään 32. Tulojen ja lähtöjen keskimääräinen lukumäärä on enintään 32. Näiden enemmän tuloja ja lähtöjä tarvitsevien piirien suunnitteluun voidaan käyttää joko lukuisia PLA: ita / PAL: ita tai muuten tyylikkäämpi tyyppi sirua voidaan käyttää nimeltään CPLD (monimutkainen ohjelmoitava logiikkalaite). CPLD-siru sisältää useita piirilohkoja yhdellä sirulla, sisäisten johdotusresurssien avulla piirilohkojen kiinnittämiseksi. Jokainen piirilohko on verrattavissa PLA: han tai PAL: iin.

Mikä on monimutkainen ohjelmoitava logiikkalaite?

CPLD: n lyhenne on 'monimutkaiset ohjelmoitavat logiikkalaitteet', se on yksi eräänlainen integroitu piiri sovellussuunnittelijat suunnittelevat toteuttavan digitaalisia laitteita, kuten matkapuhelimia. Nämä pystyvät käsittelemään tietoisesti korkeampia malleja kuin SPLD (yksinkertaiset ohjelmoitavat logiikkalaitteet), mutta tarjoavat vähemmän logiikkaa kuin FPGA ( kentän ohjelmoitavat porttiryhmät CPLD: t sisältävät lukuisia logiikkalohkoja, joista kukin sisältää 8-16 makrosolua. Koska jokainen logiikkalohko suorittaa tietyn toiminnon, kaikki logiikkalohkon makrosolut ovat täysin yhteydessä. Käytöstä riippuen nämä lohkot voivat olla yhdistettyjä toisiinsa.

Monimutkainen ohjelmoitava logiikkalaite

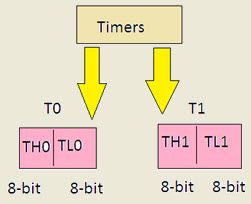

Suurimmalla osalla CPLD: itä (monimutkaiset ohjelmoitavat logiikkalaitteet) on makrosoluja, joilla on logiikkatoiminnon summa ja valinnainen FF (kiikku) . Kombinatorinen logiikkatoiminto tukee sirusta riippuen 4 - 16 tuotetermiä ja kattavan tuulettimen. CPLD: t eroavat myös vaihtorekistereiden ja logiikkaporttien suhteen. Tästä syystä CPLD: itä, joissa on valtava määrä logiikkaportteja, voidaan käyttää FPGA: iden sijaan. Toinen CPLD-spesifikaatio tarkoittaa tuotetermien lukumäärää, jonka makrosolu voi saavuttaa. Tuoteehdot ovat digitaalisten signaalien tulosta, jotka suorittavat tietyn logiikkatoiminnon.

CPLD: itä on saatavana useina IC-pakettilomakkeina ja logiikkaperheinä. CPLD: t eroavat myös syöttöjännitteestä, käyttövirrasta, valmiustilavirrasta ja tehohäviöstä. Lisäksi nämä ovat saatavana erilaisilla muistimäärillä ja erilaisilla muistituilla. Yleensä muisti ilmaistaan bitteinä / megabitteinä. Muistituki koostuu ROM-muistista, RAM-muistista ja kahden portin RAM-muistista. Se sisältää myös CAM-muistin (sisältöosoitettava muisti) sekä FIFO-muistin (ensimmäinen sisään, ensin ulos) ja LIFO (viimeinen sisään, viimeinen ulos) -muistin.

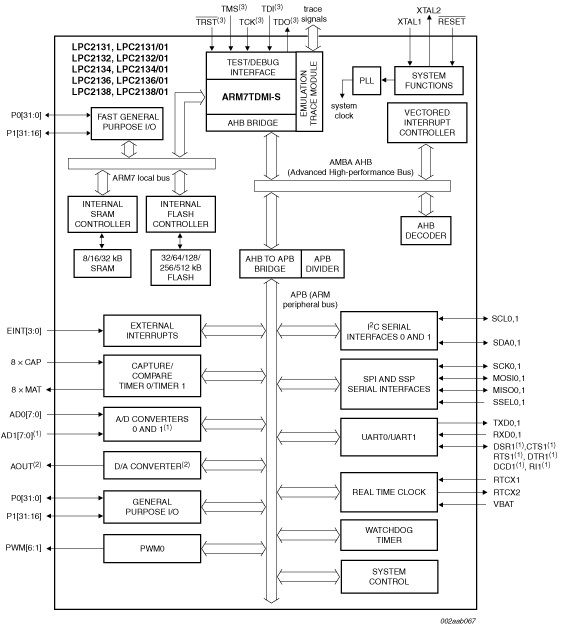

Monimutkaisen ohjelmoitavan logiikkalaitteen arkkitehtuuri

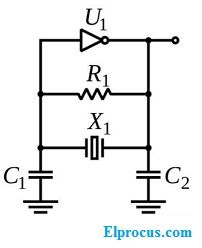

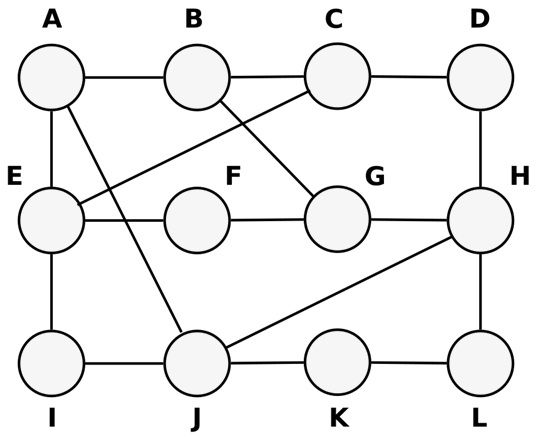

Monimutkainen ohjelmoitava logiikkalaite käsittää ryhmän ohjelmoitavia FB: itä (toiminnalliset lohkot). Näiden toiminnallisten lohkojen tulot ja lähdöt on kytketty yhteen GIM: llä (maailmanlaajuinen yhdistämismatriisi). Tämä yhdysmatriisi on konfiguroitavissa uudelleen, jotta voimme muokata toiminnallisten lohkojen välisiä kontakteja. Tulee joitakin tulo- ja lähtölohkoja, joiden avulla voimme yhdistää CPLD: n ulkomaailmaan. CPLD: n arkkitehtuuri on esitetty alla.

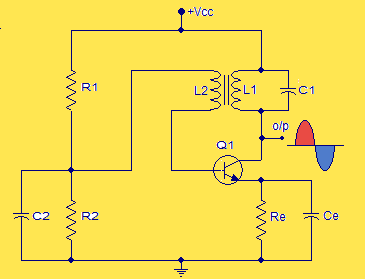

Yleensä ohjelmoitava FB näyttää joukko logiikkaportteja , jossa joukko AND-portteja voidaan ohjelmoida ja OR-portit ovat vakaita. Jokaisella valmistajalla on kuitenkin oma tapansa suunnitella toiminnallinen lohko. Lueteltu o / p löytyy toimimalla OR-portin lähdöistä saatuja takaisinkytkentäsignaaleja.

CPLD-arkkitehtuuri

CPLD-ohjelmoinnissa suunnittelu koodataan ensin Verilog- tai VHDL-kielellä, kun koodi on (simuloitu ja syntetisoitu. Synteesin aikana CPLD-malli (kohdelaite) valitaan käsin ja tuotetaan teknologiaan perustuva kartoitusverkkoluettelo. Tämä luettelo voi olla lähellä - sovittaminen aitoon CPLD-arkkitehtuuriin käyttämällä paikka- ja reittiprosessia, joka saavutetaan tyypillisesti CPLD Companyn omistaman paikan ja reitin ohjelmistolla. Sitten operaattori tekee joitain vahvistusprosesseja. Jos kaikki on hyvin, hän käyttää CPLD: tä, muuten hän järjestää sen uudelleen.

CPLD: n arkkitehtuurikysymykset

Tarkasteltaessa monimutkaista ohjelmoitavaa logiikkalaitetta suunnittelussa käytettäväksi voidaan ottaa huomioon seuraavat arkkitehtuurikysymykset

- Ohjelmointitekniikka

- Toimintolohkon ominaisuus

- I / O-ominaisuus

Jotkut CPLD-perheistä eri jälleenmyyjiltä sisältävät

- Altera MAX 7000- ja MAX 9000 -perheet

- Atmel ATF- ja ATV-perheet

- Säle isp LSI-perhe

- Ristikko (Vantis) MACH-perhe

- Xilinx XC9500 -perhe

CPLD: n perheet

CPLD: n sovellukset

CPLD-sovellukset sisältävät seuraavat

- Monimutkaiset ohjelmoitavat logiikkalaitteet ovat ihanteellisia korkean suorituskyvyn kriittisiin ohjaussovelluksiin.

- CPLD: tä voidaan käyttää digitaalisissa malleissa käynnistyslataimen toimintojen suorittamiseen

- CPLD: tä käytetään kentällä ohjelmoitavan porttiryhmän kokoonpanotietojen lataamiseen haihtumattomasta muistista.

- Yleensä niitä käytetään pienissä suunnittelusovelluksissa, kuten osoitteen purkaminen

- CPLD-levyjä käytetään usein monissa sovelluksissa, kuten kustannusherkissä, paristokäyttöisissä kannettavissa laitteissa sen pienen koon ja matalan virrankäytön vuoksi.

Näin ollen kyse on monimutkaisesta ohjelmoitavasta logiikkalaitearkkitehtuurista ja sen sovelluksista. Toivomme, että olet saanut paremman käsityksen tästä käsitteestä. Lisäksi kaikki tätä käsitettä koskevat kysymykset tai sähköisten ja elektronisten projektien toteuttamiseksi , anna arvokkaat ehdotuksesi kommentoimalla alla olevassa kommenttiosassa. Tässä on kysymys sinulle, mikä on ero CPLD: n ja FPGA: n välillä?

Valokuvahyvitykset:

- CPLD wikimedia

- CPLD: n arkkitehtuuri slidesharecdn